### VF-X100K676图像开发板

# CONTENTS 目录

- 01 Xilinx FPGA开发板介绍

- 02 XC7A100T FPGA芯片介绍

- 03 VF-X100K676 开发板介绍

- 04 VF-X100K676 Demo资料介绍

- 05 更多图片展示

https://www.szovs.com

#### 深圳市奥唯思科技有限公司

SHENZHEN OVS TECHONOGY CO.,LTD

深圳市奥唯思科技有限公司(深圳奥唯思/SZOVS)成立于2021年,公司位于深圳南山西丽,专注于**摄像头采集**与LCD图形显示,

FPGA ISP处理以及FPGA国产化方案,致力于为客户提供

可快速量产、高性价的工业、医疗解决方案。

Verilog HDL关键字

争做一流的FPGA图像方案供应商

#### 资质荣誉

凭着FPGA行业十几年的技术积累,致力于一流的FPGA图像方案供应商,奥唯思帮客户快速方案落地,为**影石(insta360)、易灵思、高云、Lattice、思特威、中科院**等知名企业提供FPGA图像解决方案,得到了市场广泛的认可……

奥唯思,为FPGA图像而生.....

# O 1 PART

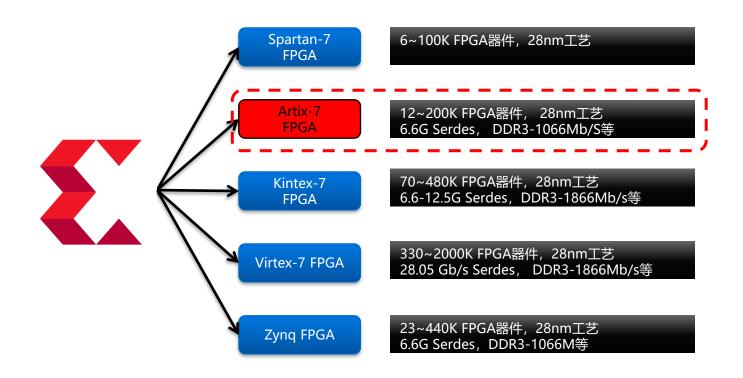

## Xilinx FPGA开发板介绍

#### FPGA开发板产品-赛灵思相关

VF-X25K225 赛灵思<mark>S7</mark> FPGA图像开发板

VF-X100K676 赛灵思A7 FPGA图像开发板

VF-X70K676 赛灵思K7 FPGA图像开发板

VF-ZYNQ7020 赛灵思ZYNQ FPGA开发板

| <b>型号</b>                  | 系列       | 资源           | 存储     | DVP<br>相机 | MIPI<br>相机 | 图像<br>接口                      | 通信接口                              | 特性描述                               |

|----------------------------|----------|--------------|--------|-----------|------------|-------------------------------|-----------------------------------|------------------------------------|

| VF-X25K255                 | Spartan7 | 25K          | DDR3   | <b>√</b>  |            | HDMI, LVDS, RGB<br>子卡         | UART<br>USB2.0卡                   | 配套《FPGA图像》1书<br>入门级25K FPGA开发板     |

| VF-X100K676<br>VF-X200K676 | Artix7   | 100K<br>200K | DDR3*2 | √         | √<br>双目    | HDMI, LVDS<br>MIPI CSI, RGB子卡 | UART PCIE2.0<br>SFP USB3.0<br>以太网 | 配套《FPGA图像》1书<br>进阶100/200K FPGA开发板 |

| VF-X70K676                 | Kintex7  | 70K          | DDR3*2 | √<br>双目   |            | HDMI, LVDS<br>RGB子卡           | UART PCIE2.0<br>SFP               | 配套《FPGA图像》1书<br>进阶70K FPGA开发板      |

| VF-ZYNQ7020                | ZYNQ     | 85K          | DDR3   | V         | √          | RGB<br>HDMI                   | UART<br>以太网                       | 入门ZYNQ图像处理<br>完整的MIPI解决方案          |

| 型号          | 厂家     | 色彩       | 靶面    | 像素     | 分辨率       | 曝光 | 帧率  | 接口          | 镜头  | 焦距    | 特性                        |

|-------------|--------|----------|-------|--------|-----------|----|-----|-------------|-----|-------|---------------------------|

| VS-SC233HGS | 思特威    | 黑白       | 1/2.6 | 3.0um  | 1920*1080 | 全局 | 120 | MIPI        | M12 | 3.6mm | 全局、高速、1080P               |

| VS-SC130GS  | 思特威    | 黑白<br>彩色 | 1/2.7 | 4um    | 1280*1024 | 全局 | 240 | DVP<br>MIPI | M12 | 3.6mm | 全局、高速、低照度                 |

| VS-SC2210   | 思特威    | 彩色       | 1/1.8 | 4um    | 1920*1080 | 卷帘 | 60  | MIPI        | M12 | 6mm   | 大靶面、低照度                   |

| VS-SC200AI  | 思特威    | 彩色       | 1/2.8 | 2.9um  | 1920*1080 | 卷帘 | 60  | MIPI        | M12 | 3.6mm | HDR, 低照度                  |

| VS-SC1336   | 思特威    | 彩色       | 1/3   | 3.75um | 1280*720  | 卷帘 | 60  | DVP         | M12 | 4mm   | 低成本、720P                  |

| VS-AR0135   | Aptina | 黑白       | 1/3   | 3.75um | 1280*1024 | 全局 | 60  | DVP         | M12 | 3.6mm | 全局黑白、车规                   |

| VS-MT9V034  | Micron | 黑白       | 1/3   | 6um    | 752*480   | 全局 | 60  | DVP         | CS  | 4mm   | 全局、 <mark>850nm</mark> 敏感 |

| VS-MT9M001  | Micron | 彩色       | 1/2   | 5.2um  | 1280*1024 | 卷帘 | 30  | DVP         | M12 | 8mm   | 大靶面、低成本                   |

# 02 PART

### XC7A100T FPGA 芯片介绍

#### **Artix-7 FPGAs**

| (1.0V, 0.95V, 0.9V) |                                                        |             |             |             |             |             |             |             |             |

|---------------------|--------------------------------------------------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|

|                     | Part Number                                            | XC7A12T     | XC7A15T     | XC7A25T     | XC7A35T     | XC7A50T     | XC7A75T     | XC7A100T    | XC7A200T    |

|                     | Logic Cells                                            | 12,800      | 16,640      | 23,360      | 33,280      | 52,160      | 75,520      | 101,440     | 215,360     |

| Logic<br>Resources  | Slices                                                 | 2,000       | 2,600       | 3,650       | 5,200       | 8,150       | 11,800      | 15,850      | 33,650      |

| Resources           | CLB Flip-Flops                                         | 16,000      | 20,800      | 29,200      | 41,600      | 65,200      | 94,400      | 126,800     | 269,200     |

|                     | Maximum Distributed RAM (Kb)                           | 171         | 200         | 313         | 400         | 600         | 892         | 1,188       | 2,888       |

| Memory<br>Resources | Block RAM/FIFO w/ ECC (36 Kb each)                     | 20          | 25          | 45          | 50          | 75          | 105         | 135         | 365         |

| Resources           | Total Block RAM (Kb)                                   | 720         | 900         | 1,620       | 1,800       | 2,700       | 3,780       | 4,860       | 13,140      |

| Clock Resources     | CMTs (1 MMCM + 1 PLL)                                  | 3           | 5           | 3           | 5           | 5           | 6           | 6           | 10          |

| I/O Resources       | Maximum Single-Ended I/O                               | 150         | 250         | 150         | 250         | 250         | 300         | 300         | 500         |

| i/O Resources       | Maximum Differential I/O Pairs                         | 72          | 120         | 72          | 120         | 120         | 144         | 144         | 240         |

|                     | DSP Slices                                             | 40          | 45          | 80          | 90          | 120         | 180         | 240         | 740         |

|                     | PCle® Gen2 <sup>(1)</sup>                              | 1           | 1           | 1           | 1           | 1           | 1           | 1           | 1           |

| Embedded<br>Hard IP | Analog Mixed Signal (AMS) / XADC                       | 1           | 1           | 1           | 1           | 1           | 1           | 1           | 1           |

| Resources           | Configuration AES / HMAC Blocks                        | 1           | 1           | 1           | 1           | 1           | 1           | 1           | 1           |

|                     | GTP Transceivers (6.6 Gb/s Max<br>Rate) <sup>(2)</sup> | 2           | 4           | 4           | 4           | 4           | 8           | 8           | 16          |

|                     | Commercial Temp (C)                                    | -1, -2      | -1, -2      | -1, -2      | -1, -2      | -1, -2      | -1, -2      | -1, -2      | -1, -2      |

| Speed Grades        | Extended Temp (E)                                      | -2L, -3     |

|                     | Industrial Temp (I)                                    | -1, -2, -1L |

|                     | Dissessions Bell Bitch                                 | -, -,       | -, -,       | _, _,       | _, _,       | -, -,       | -, -,       |             | _, _,       |

Transceiver Optimization at the Lowest Cost and Highest DSP Bandwidth

|            | Package <sup>(3), (4)</sup> | Dimensions<br>(mm) | Ball Pitch<br>(mm) | Available User I/O: 3.3V SelectIO™ HR I/O (GTP Transceivers) |         |         |         |         |         |         |          |

|------------|-----------------------------|--------------------|--------------------|--------------------------------------------------------------|---------|---------|---------|---------|---------|---------|----------|

|            | CPG236                      | 10 x 10            | 0.5                |                                                              | 106 (2) |         | 106 (2) | 106 (2) |         |         |          |

|            | CPG238                      | 10 x 10            | 0.5                | 112 (2)                                                      |         | 112 (2) |         |         |         |         |          |

|            | CSG324                      | 15 x 15            | 0.8                |                                                              | 210 (0) |         | 210 (0) | 210 (0) | 210 (0) | 210 (0) |          |

|            | CSG325                      | 15 x 15            | 0.8                | 150 (2)                                                      | 150 (4) | 150 (4) | 150 (4) | 150 (4) |         |         |          |

|            | FTG256                      | 17 x 17            | 1.0                |                                                              | 170 (0) |         | 170 (0) | 170 (0) | 170 (0) | 170 (0) |          |

|            | SBG484                      | 19 x 19            | 0.8                |                                                              |         |         |         |         |         |         | 285 (4)  |

| Footprint  | FGG484 <sup>(5)</sup>       | 23 x 23            | 1.0                |                                                              | 250 (4) |         | 250 (4) | 250 (4) | 285 (4) | 285 (4) |          |

| Compatible | FBG484 <sup>(5)</sup>       | 23 x 23            | 1.0                |                                                              |         |         |         |         |         |         | 285 (4)  |

| Footprint  | FGG676 <sup>(6)</sup>       | 27 x 27            | 1.0                |                                                              |         |         |         |         | 300 (8) | 300 (8) |          |

| Compatible | FBG676 <sup>(6)</sup>       | 27 x 27            | 1.0                |                                                              |         |         |         |         |         |         | 400 (8)  |

|            | FFG1156                     | 35 x 35            | 1.0                |                                                              |         |         |         |         |         |         | 500 (16) |

# O3 PART

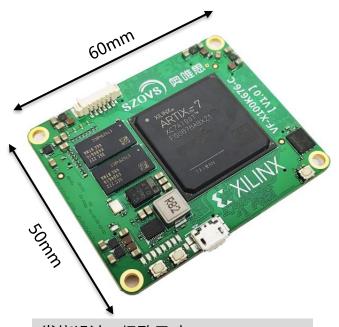

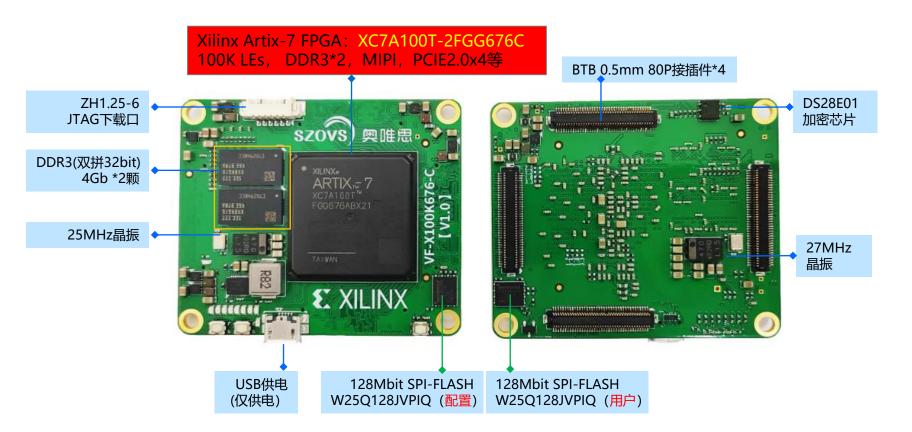

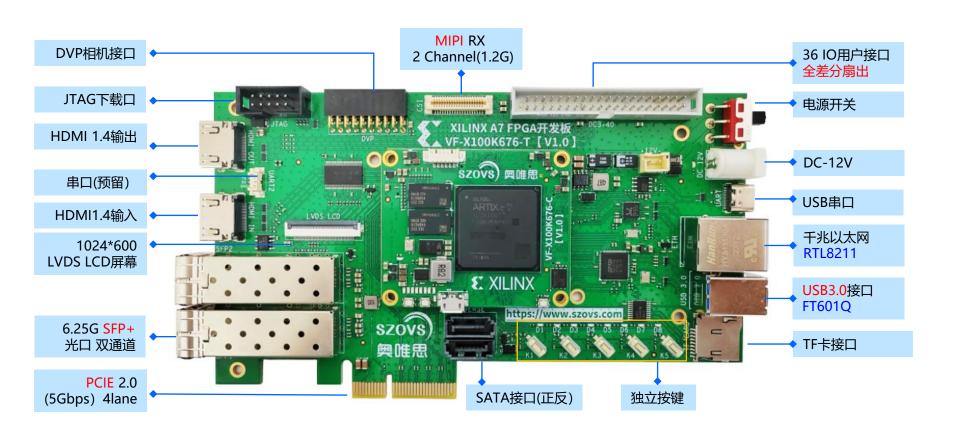

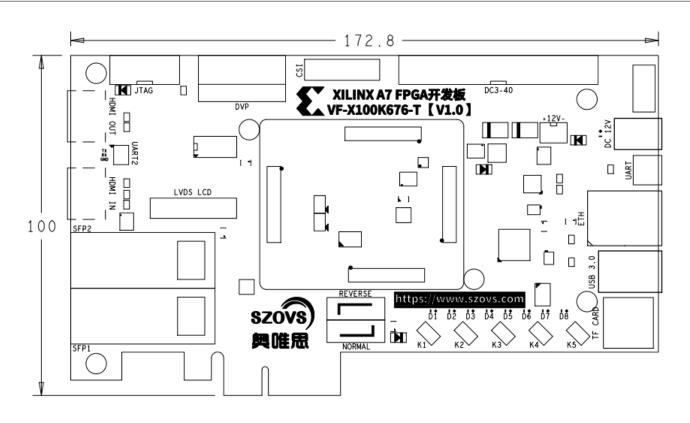

## VF-X100K676 开发板介绍

发烧设计,极致尺寸; 工匠品质,为FPGA而生

| 参数      | 描述                                        |

|---------|-------------------------------------------|

| 供应商     | 奥唯思 科技                                    |

| 核心板型号   | VF-X100K676-C                             |

| FPGA厂家  | Xilinx (赛灵思) Artix-7系列                    |

| FPGA型号  | XC7A100T-2FGG676                          |

| FPGA资源  | 100K 逻辑单元, 6.25G Serdes, DDR3 IP, PCIE2.0 |

| DDR3存储  | 4G 16bit*2颗 DDR3: K4B4G1646E              |

| PCBA尺寸  | 60mm *50mm                                |

| PCB工艺   | 8层 1.6mm 沉金 亚黑                            |

| 板载FLASH | 128Mbit SPI FLASH: W25Q128JVPIQ           |

| 用户FLASH | 128Mbit SPI FLASH: W25Q128JVPIQ           |

| 板子外设    | 2个用户按键,1个USB供电口,8个测试LED                   |

| 其他接口    | 板载ZH1.25-6 JTAG下载口                        |

| B2B接口   | 4个0.5mm双排80P B2B接插件 (母座*4)                |

| 供电      | 集成USB Mini供电口   B2B接插件输入5V DC             |

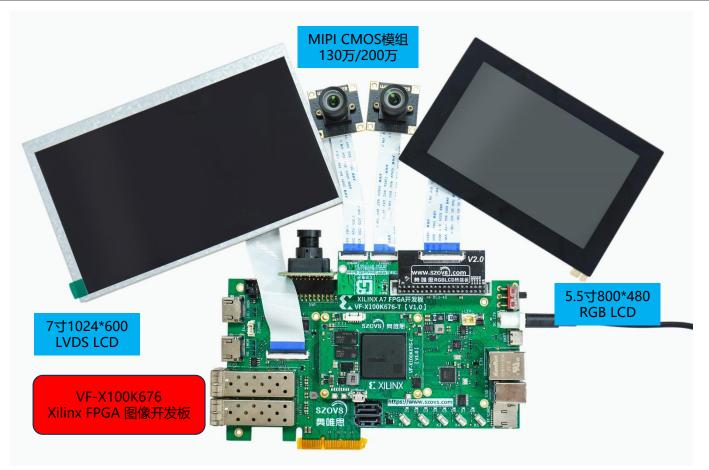

参数 描述 供应商 奥唯思 科技 核心板型号 VF-X100K676 FPGA厂家 Xilinx (赛灵思) Artix-7系列 FPGA型号 XC7A100T-2FGG676C FPGA资源 100K 逻辑单元, 6.25G Serdes, DDR3 IP, PCIE2.0 千兆太网接口 基于RTL8211 PHY, 支持100/1000M以太网通信 USB3.0接口 基于FTDI的FT601Q, 支持USB3.0/2.0通信 基于FPGA Serdes,支持2路6.25Gbps 光口通信 SFP光口 HDMI 输入 基于FPGA TMDS, 最高支持1080P60 HDMI 输出 基于FPGA TMDS, 最高支持1080P60 DVP相机接口 支持奥唯思全系列DVP相机,包括OV5640、MT9V034、 AR0135、SC130GS等3.3V DVP模组 MIPI RX接口 支持奥唯思全系列MIPI相机,包括SC130GS、SC2210、 SC200AI、SC235HGS等MIPI模组

终极FPGA图像图像开发板

其他特色

平台包含了UART、SPI、I2C、TF Card 、GPIO(LED/KEY) 等RSIC-V必备的外设,无缝支持 RISC-V FPGA原型验证平台

# O4 PART

### FPGA开发板 Demo资料介绍

#### FPGA开发板 基础Demo介绍

| 序号 | 工程名                      | 设计描述                  |

|----|--------------------------|-----------------------|

| 1  | 01_LED_8bit_Test         | LED流水灯测试实验(核心板)       |

| 2  | 02_KEY_2bit_Test         | 独立按键测试实验(核心板)         |

| 3  | 03_FPGA_UART_Test_Bottom | UART串口测试实验            |

| 4  | 04_FPGA_DDR3_Test        | DDR3读写测试实验(核心板)       |

| 5  | 05_RGBLCD_Test_800480    | 800*480 RGBLCD显示实验    |

| 6  | 06_LVDS_LCD_Test_1024600 | 1024*600 LVDS LCD显示实验 |

| 7  | 07_HDMI_Disp_Test_720P   | 1280*720@60 HDMI显示实验  |

| 8  | 08_HDMI_Disp_Test_1080P  | 1920*1080@60 HDMI显示实验 |

| 9  | 09_FT601_USBSS_Test      | FT601 USB3.0通路测试实验    |

| 10 | 10_RGMII_Eth_Test        | RGMII 读写测试实验          |

| 11 | 11_PCle_Test             | PCIE2.0 Linkup测试实验    |

| 12 | 12_SFP_Test              | 6.25Gbps SFP回环测试实验    |

#### FPGA开发板 摄像头Demo

| 序号 | 工程名                                  | 设计描述                                            |

|----|--------------------------------------|-------------------------------------------------|

| 1  | 01-1_CMOS_AR0135_HDMI_720P           | 基于AR0135 DVP相机的HDMI屏720P成像案例                    |

| 2  | 01-2_CMOS_AR0135_RGBLCD_800480       | 基于AR0135 DVP相机的RGB屏(800*480)成像案例                |

| 3  | 02-1_CMOS_SC130GS_Gray_HDMI_720P     | 基于SC130S MIPI 4lane相机的HDMI屏720P成像案例             |

| 4  | 02-2_CMOS_SC130GS_Gray_LVDS_1024600  | 基于SC130S MIPI 4lane相机的LVDS屏(1024*600)成像案例       |

| 5  | 02-3_CMOS_SC130GS_Gray_RGBLCD_800480 | 基于SC130S MIPI 4lane相机的RGB屏(800*480)成像案例         |

| 6  | 03-1_CMOS_SC2210_HDMI_1080P          | 基于SC2210 MIPI 4lane相机的HDMI屏1080P成像案例            |

| 7  | 03-2_CMOS_SC2210_LVDS_1024600        | 基于SC2210 MIPI 4lane相机的LVDS屏(1024*600)成像案例       |

| 8  | 03-3_CMOS_SC2210_RGB_800480          | 基于SC2210 MIPI 4lane相机的MIPI DSI屏(1024*600)成像案例   |

| 9  | 04-1_CMOS_SC233HGS_HDMI_1080P        | 基于SC233HGS MIPI 4lane相机的HDMI屏1080P成像案例          |

| 10 | 04-2_CMOS_SC233HGS_LVDS_1024600      | 基于SC233HGS MIPI 4lane相机的LVDS屏(1024*600)成像案例     |

| 11 | 04-3_CMOS_SC233HGS_RGB_800480        | 基于SC233HGS MIPI 4lane相机的MIPI DSI屏(1024*600)成像案例 |

备注: DVP与LVDS不能同时用,因此AR0135没有LVDS LCD工程

#### FPGA开发板 图像Demo介绍 (AR0135+SC130GS黑白)

| 序号 | 工程名                        | 设计描述                     |

|----|----------------------------|--------------------------|

| 1  | 3.1_Histgram_EQ            | 直方图均衡算法FPGA加速            |

| 2  | 3.2_Image_Constrast        | 对比度增强算法FPGA加速            |

| 3  | 3.3_Gamma_Mapping          | Gamma映射算法FPGA加速          |

| 4  | 4.1_Avg_Filter             | 均值滤波算法FPGA加速             |

| 5  | 4.2_Med_Filter             | 中值滤波算法FPGA加速             |

| 6  | 4.3_Gaussian_Filter        | 高斯滤波算法FPGA加速             |

| 7  | 4.4_Bilateral_Filter       | 双边滤波算法FPGA加速             |

| 8  | 5.3_Region_Binarization    | 局部阈值二值化算法FPGA加速          |

| 9  | 5.4_Sobel_Edge_Detector    | Sobel边缘检测算法FPGA加速        |

| 10 | 5.5_Bin_Erosion_Dilation   | 腐蚀、膨胀算法FPGA加速            |

| 11 | 5.6_Frame_Difference_Test  | 基于帧间差的运动追踪算法FPGA加速       |

| 12 | 6.2_Robert_Sharpen         | 基于Robert算子锐化算法FPGA加速     |

| 13 | 6.3_Sobel_Sharpen          | 基于Sobel算子锐化算法的FPGA加速     |

| 14 | 6.4_Laplacian_Sharpen      | 基于Laplacian算子锐化算法的FPGA加速 |

| 15 | 7.1_Nearest_Interpolation  | 最近邻域插值缩放算法的FPGA加速        |

| 16 | 7.2_Bilinear_Interpolation | 双线性插值缩放算法的FPGA加速         |

| 17 | 8.1_Lenet_Test             | Lenet5手写数字识别             |

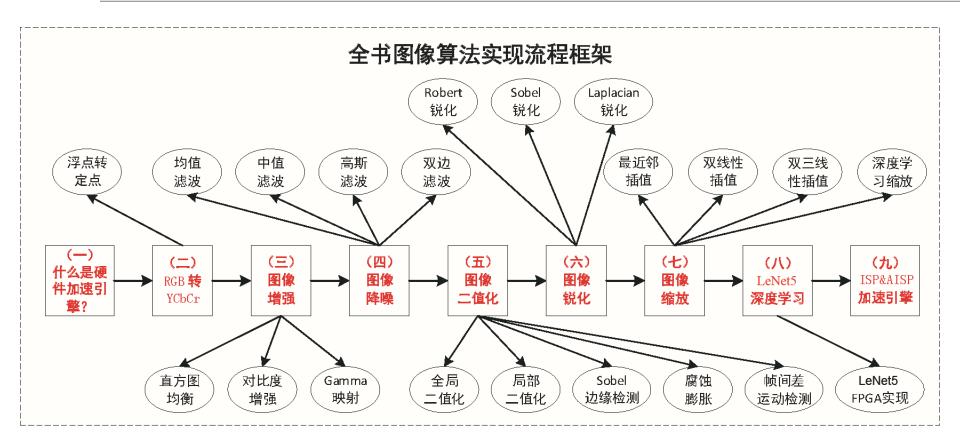

#### 配套《基于MATLAB与FPGA的图像处理》

#### 目录

- 第1章 什么是硬件加速引擎

- 第2章 RGB转YCbCr算法介绍及MATLAB与FPGA实现

- 第3章 常用图像增强算法介绍及MATLAB与FPGA实现

- 第4章 常用图像降噪算法介绍及MATLAB与FPGA实现

- 第5章 常用图像二值化算法介绍及MATLAB与FPGA实现

- 第6章 常用图像锐化算法介绍及MATLAB与FPGA实现

- 第7章 常用图像缩放算法介绍及MATLAB与FPGA实现

- 第8章 基于LeNet5的深度学习算法介绍及MATLAB与FPGA实现

- 第9章 传统ISP及AISP的图像处理硬件加速引擎介绍

- 国内第一本基于MATLAB/FPGA的图像处理教程

- FPGA图像算法硬件加速进阶(中级学者)

- **2024已累积销售近万本**,受广泛好评

- 目前已经被多家高校选定,作为大学教材

- Bilibili连载视频教程(基于本FPGA开发板)

#### FPGA终点: 图像算法开发

#### FPGA开发板 套餐介绍

可选

可选

1024\*600 LVDS/RGB液晶屏

800\*480 RGB IPS触摸屏

AR0135 130万全局黑白

SC130GS 130万全局黑白

SC2210 200万卷帘彩色

SC233HGS 200万全局黑白

# 05 PART

## 更多图片展示

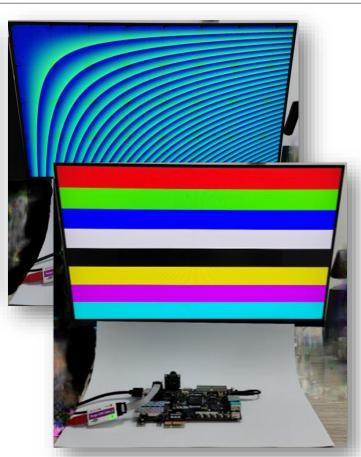

#### 基于DDR3的HDMI 1080P显示Demo

#### 测试场景介绍:

DDR3:800MHz (2颗)HDMI输出: LVDS模拟1920\*1080@60输出图像

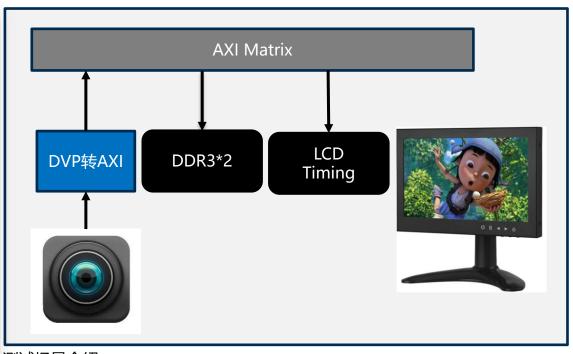

#### 基于SC130GS/SC2210的实时HDMI 720P/1080P60显示

#### 测试场景介绍:

1) SC130GS: 1280\*720@60黑白全局曝光相机 2) SC2210: 1920\*1080@60彩色卷帘曝光相机 3) DDR3+HDMI: AXI总线+720P/1080P RGB输出

#### 深圳奥唯思,为FPGA图像而生......

奥唯思 官方公众号

**官方网站**: <u>www.szovs.com</u> (资料下载)

官方淘宝: szovs.taobao.com

"奥唯思FPGA" 店铺

FPGA论坛: www.crazyfpga.com

FPGA交流群: <u>851598171</u> (QQ)